## Evaluation of stress voltage on off-state time-dependent breakdown for GaN MIS-HEMT with $SiN_x$ gate dielectric<sup>\*</sup>

Tao-Tao Que(阙陶陶)<sup>1</sup>, Ya-Wen Zhao(赵亚文)<sup>1</sup>, Qiu-Ling Qiu(丘秋凌)<sup>1</sup>, Liu-An Li(李柳暗)<sup>1</sup>, Liang He(何亮)<sup>2</sup>, Jin-Wei Zhang(张津玮)<sup>1</sup>, Chen-Liang Feng(冯辰亮)<sup>1</sup>, Zhen-Xing Liu(刘振兴)<sup>1</sup>, Qian-Shu Wu(吴千树)<sup>1</sup>, Jia Chen(陈佳)<sup>1</sup>, Cheng-Lang Li(黎城朗)<sup>1</sup>, Qi Zhang(张琦)<sup>1</sup>, Yun-Liang Rao(饶运良)<sup>1</sup>, Zhi-Yuan He(贺致远)<sup>3</sup>, and Yang Liu (刘扬)<sup>1,†</sup>

<sup>1</sup> School of Electronics and Information Technology, Sun Yat-Sen University, Guangzhou 510275, China

<sup>2</sup> School of Materials Science and Engineering, Sun Yat-Sen University, Guangzhou 510275, China

<sup>3</sup> Science and Technology on Reliability Physics and Application of Electronic Component Laboratory,

No. 5 Electronics Research Institute of the Ministry of Industry and Information Technology, Guangzhou 510610, China

(Received 3 July 2020; revised manuscript received 10 August 2020; accepted manuscript online 13 August 2020)

Stress voltages on time-dependent breakdown characteristics of GaN MIS-HEMTs during negative gate bias stress (with  $V_{GS} < 0$ ,  $V_D = V_S = 0$ ) and off-state stress ( $V_G < V_{Th}$ ,  $V_{DS} > 0$ ,  $V_S = 0$ ) are investigated. For negative bias stress, the breakdown time distribution ( $\beta$ ) decreases with the increasing negative gate voltage, while  $\beta$  is larger for higher drain voltage at off-state stress. Two humps in the time-dependent gate leakage occurred under both breakdown conditions, which can be ascribed to the dielectric breakdown triggered earlier and followed by the GaN layer breakdown. Combining the electric distribution from simulation and long-term monitoring of electric parameter, the peak electric fields under the gate edges at source and drain sides are confirmed as the main formation locations for per-location paths during negative gate voltage stress and off-state stress, respectively.

**Keywords:** gallium nitride, LPCVD-SiN $_x$  MIS-HEMT, time-dependent breakdown, negative gate bias, offstate stress

PACS: 72.80.Ey, 72.80.Sk, 73.20.At, 77.22.Jp

#### 1. Introduction

GaN-based electronic materials are considered as excellent candidates for power switching applications, owning to their outstanding properties such as high electrical breakdown field and high saturated electron mobility.<sup>[1,2]</sup> As for Al-GaN/GaN metal-insulator-semiconductor high electron mobility transistor (MIS-HEMT), silicon nitride  $(SiN_x)$  dielectric deposited by low pressure chemical deposition (LPCVD) technique offers the absence of the Ga-O bonds and a large conduction band offset ( $\Delta E_c = 2.3$  eV), yielding an effectively suppressed gate leakage and a large gate swing.<sup>[3–5]</sup> In addition, the free plasma-induced damage and high deposition temperature (780 °C) provide a high quality dielectric film with low defect density,<sup>[6]</sup> thus offering excellent thermal stability and large forward breakdown electric field (14 MV/cm).<sup>[7]</sup> However, long term stability and reliability for GaN MIS-HEMT with LPCVD SiN<sub>x</sub> gate dielectric still need extensive evaluation before commercial deployment.

The GaN MIS-HEMT is often adopted in cascode configuration, requiring a negative gate bias to deplete the twodimensional electron gas (2DEG) channel and sustain the off-

#### **DOI:** 10.1088/1674-1056/abaed8

state high drain voltage.<sup>[8,9]</sup> Marcon et al.<sup>[10]</sup> have revealed that the off-state breakdown is time-dependent and even a small voltage stress can trigger hard breakdown after a sufficient time stress. Furthermore, the effects of ultraviolet light and substrate bias on the time-dependent breakdown (TDB) were also evaluated previously.<sup>[11,12]</sup> Generally, the absolute value of negative gate bias is relatively smaller than that of drain voltage under off-state stress condition. However, both negative gate bias and drain voltage are accelerated factors which will inevitably bring defects inside the gate dielectric and GaN materials, and eventually cause catastrophic failure of devices.<sup>[9,10]</sup> In the enhance-mode LPCVD-SiN<sub>x</sub>/GaN MIS-FET, Hua et al.<sup>[13]</sup> found that the threshold voltage stability shows an obvious dependence on the negative gate bias under reverse-bias step-stress. Until now, researchers have been mainly focusing on electron detrapping process in the gate dielectric induced by moderate negative gate stress with the overdrive voltage  $(V_{\rm GS} - V_{\rm Th})$  smaller than -80 V.<sup>[14]</sup> The negative gate stress condition can be regarded as special offstate stress with a certain large drain to gate voltage  $(V_{DG})$ bias, which is also able to cause breakdown of gate dielec-

<sup>†</sup>Corresponding author. E-mail: liuy69@mail.sysu.edu.cn

http://iopscience.iop.org/cpb http://cpb.iphy.ac.cn

<sup>\*</sup>Project supported by the National Key Research and Development Program, China (Grant No. 2017YFB0402800), the Key Research and Development Program of Guangdong Province, China (Grant Nos. 2019B010128002 and 2020B010173001), the National Natural Science Foundation of China (Grant No. U1601210), the Natural Science Foundation of Guangdong Province, China (Grant No. 2015A030312011), the Open Project of Key Laboratory of Microelectronic Devices and Integrated Technology (Grant No. 202006), the Science and Technology Plan of Guangdong Province, China (Grant No. 2017B010112002), and the China Postdoctoral Science Foundation (Grant No. 2019M663233).

<sup>© 2020</sup> Chinese Physical Society and IOP Publishing Ltd

tric or GaN materials. However, there are no reports on comparing time-dependent breakdown between off-state stress and negative bias stress, which is obviously beneficial for further understanding the inherent physical mechanism.

In this paper, rapid breakdown of GaN MIS-HEMT with LPCVD  $SiN_x$  gate dielectric under negative gate bias stress  $(V_{\text{GS}} < 0 \text{ V}, V_{\text{DS}} = 0 \text{ V})$  and off-state stress  $(V_{\text{G}} < V_{\text{Th}}, V_{\text{DS}} > 0)$ is investigated by using static constant voltage stress (CVS) The substrate and source in both stress cases are tests. grounded ( $V_{\rm S} = V_{\rm Sub} = 0$ ). The purpose of setting the two type stress conditions is to analyze the influence of  $V_{GS}$  and  $V_{DS}$  on breakdown process under a fixed drain to gate voltage  $(V_{DG})$ separately. Simulation method is utilized to further analyze the underlying degradation mechanism of the two type stress conditions. After rapid breakdown tests mentioned above, a large drain to gate voltage stress (in this paper,  $V_{DG} = 200 \text{ V}$ ) sufficient to generate large numbers of defects but not enough to cause rapid breakdown of device is selected to monitor the long-term evolution of electric parameters, which is beneficial for further underlying the inherent mechanism of the two stress conditions.

#### 2. Device details

The devices used in this paper are manufactured on the standard CMOS production line. The metal–organic chemical vapor deposition (MOCVD) GaN epitaxial layer was grown on a 6-inch (111) Si substrate (1 inch = 2.54 cm), from bottom to top is a 4-µm GaN buffer, a 300-nm/25-nm AlGaN/GaN

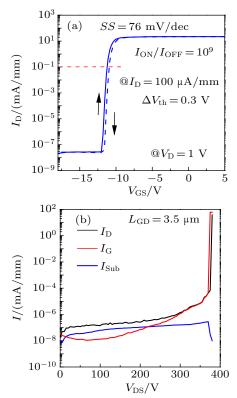

**Fig. 1.** (a) Transfer and (b) off-state blocking voltage characteristics of the GaN MIS-HEMT.

heterojunction and a 2-nm GaN cap. A 0.7-nm AlN interlayer is sandwiched between the AlGaN/GaN heterojunction. The device features a dimension of  $L_g/L_{gs}/L_{gd}/W_g$  at 3-µm/3.5-µm/100-µm. A 35-nm SiN<sub>x</sub> was deposited by LPCVD as the the gate dielectric as well as the first passivation layer. More process details are illustrated in our previous works.<sup>[15]</sup>

Figure 1 shows the transfer and off-state breakdown characteristics of devices used in this work. The devices deliver excellent gate control ability with a small subthreshold swing of 87 mV/decade and a high on/off current ratio of 10<sup>9</sup>. The threshold voltage ( $V_{\text{Th}}$ ) is approximately -10 V, which is defined at drain current of 10 µA/mm with drain voltage ( $V_{\text{DS}}$ ) of 1 V. The hysteresis of  $V_{\text{Th}}$  is small at the maximum sweep gate voltage ( $V_{\text{GS}}$ ) of 10 V. The drain to gate breakdown voltage ( $V_{\text{DG}\text{-max}}$ ) is 360 V with  $V_{\text{G}} = V_{\text{Th}} - 5$  V and  $V_{\text{S}} = V_{\text{Sub}} = 0$ . It worth noting that the drain current is mainly determined by the gate leakage current.

### 3. Results and discussion

# 3.1. Time-dependent breakdown during negative gate bias and off-state stress

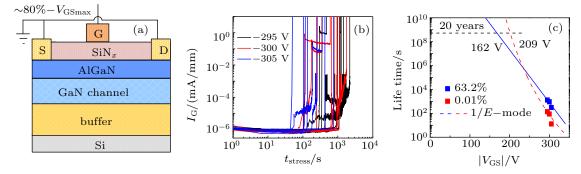

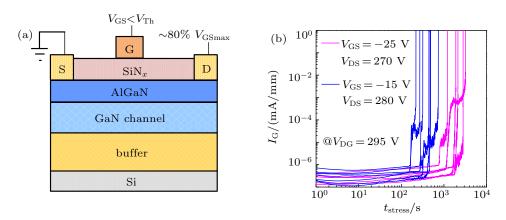

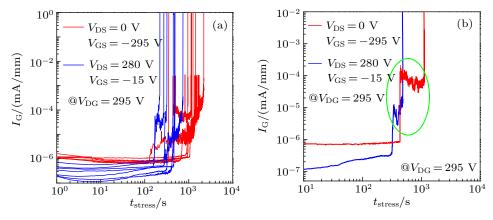

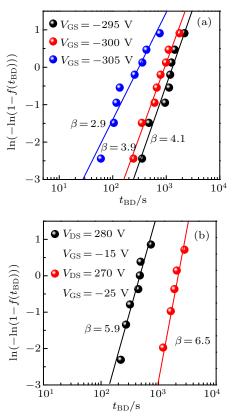

The selection of drain to gate breakdown voltage  $(V_{DG})$ is around 80% of V<sub>DG\_max</sub>, and seven devices per group of breakdown voltage are adopted. The TDB during negative bias stress is shown in Fig. 2(a), time to breakdown  $(t_{BD})$ is defined at the point when  $I_{GS}$  exceeds  $10^{-2}$  mA/mm, lifetime extrapolation of absolute  $V_{GS}$  for 20 years based on 1/Emodel<sup>[7]</sup> with failure rate of 63.2% and 0.01% are 209 V and 162 V, respectively (Fig. 2(b)). Therefore,  $SiN_x$  dielectric deposited by LPCVD delivering excellent long-term negative bias breakdown property. For off-state stress condition with a fixed drain to source voltage ( $V_{DG} = 295$  V, same as the negative bias stress),  $t_{BD}$  is approximately 1 order of magnitude shorter for  $V_{\text{DS}} = 280$  V than that of  $V_{\text{DS}} = 270$  V (Fig. 3), which is mainly account of the more sever ionizing collision of hot electron effect in gate to drain access region.<sup>[16]</sup> Furthermore, the comparison between negative gate voltage stress  $(V_{\rm GS} = -295 \text{ V}, V_{\rm DS} = 0 \text{ V})$  and off-state stress  $(V_{\rm GS} = -15 \text{ V},$  $V_{\rm DS} = 280$  V) on time-dependent breakdown indicates that the mean  $t_{BD}$  is just 0.5 order of magnitude shorter for off-state stress (Fig. 4(a)). The possible reason of this phenomenon is ascribed to that the external voltage under both bias conditions is sustained by the dielectric and depletion region in GaN layers between gate and drain electrodes. Besides, unlike the forward bias time-dependent breakdown process, [7,17-20] two sudden increasing trend in IGS occurs during both off-state and negative bias stress conditions (Fig. 4(b)). The lower  $I_{GS}$  for off-state stress (Fig. 4(a)) reflects the difference of leakage paths between the two stress conditions, the inherent mechanism will be discussed in Subsection 3.2. We previously confirm that the forward breakdown voltage of GaN MIS-HEMT with LPCVD  $SiN_x$  dielectric used in this paper is 45 V. When the maximum of electric field applied in the dielectric exceeds

11.4 MV/cm, the breakdown will be triggered in dielectric first. Then, most of the voltage is sustained by the GaN epi-taxial layer and causes the second breakdown.

Fig. 2. (a) Test diagrams of negative bias stress and (b) time-dependent breakdown with  $V_{GS} = -295$  V, -300 V, -305 V, respectively, and (c) lifetime extrapolation for 20 years based on 1/E model with failure rate of 63.2% and 0.01%.

Fig. 3. (a) Test diagrams of off-state stress and (b) time-dependent breakdown during off-state stress with  $V_{DS} = 280$  V and  $V_{DS} = 270$  V @ $V_{DG} = 295$  V.

Fig. 4. (a) The comparison of time-dependent breakdown between negative gate voltage stress and off-state stress. (b) Two sudden increasing trends of gate leakage occur during both stress conditions.

The  $t_{BD}$  of MIS-HEMT for the two stress conditions both follow a Weibull failure distribution, which can be described as

$$F(t) = 1 - \exp\left[-\left(\frac{t-\gamma}{\eta}\right)\right],\tag{1}$$

where t is the time,  $\beta$  is the shape parameter,  $\eta$  is the scale factor of 63.2% value, is defined as burn-in time or time delay, assuming  $\gamma = 0$ , equation (1) can be expressed as

in the semi-log plot of  $\ln[-\ln(1-F(t))]$  versus  $t_{BD}$ ,  $\beta$  and  $\ln(\eta)$  represent slope and intercept, respectively. The shape parameter  $\beta$  is an indicator of breakdown time distribution, which has strong relationship with the number of new defects needed for the formation of per-location paths along the device width in the material.<sup>[11,19]</sup> Indeed,

$$\beta = m \times N, \tag{3}$$

$$\ln[-\ln(1-F(t))] = \beta \ln(t) - \beta \ln(\eta)$$

where m is the defects generation rate and N represents number of traps needed for the formation of a per-location

(2)

paths.<sup>[8,21]</sup> For negative gate bias stress,  $\beta$  decreases with the increase of negative gate voltage (as shown in Fig. 5(a),  $\beta = 4.1$  for  $V_{\text{GS}} = -295$  V,  $\beta = 3.9$  for  $V_{\text{GS}} = -300$  V and  $\beta = 2.1$  for  $V_{\text{GS}} = -305$  V, respectively). The negative gate bias can fully deplete the 2DEG and GaN layers, then the generation rates of different bias voltages are nearly constant.

Fig. 5. Breakdown time distribution ( $\beta$ ) of (a) negative gate bias with  $V_{\text{GS}} = -295 \text{ V}, -300 \text{ V}, -305 \text{ V}$ , respectively and (b) off-state stress with  $V_{\text{DS}} = 280 \text{ V}$  and  $V_{\text{DS}} = 270 \text{ V}$  @ $V_{\text{DG}} = 295 \text{ V}$ .

However, more electrons will inject into the dielectric and introduce more defects under a higher bias, which means that fewer formed defects are needed for the per-location paths for higher negative gate bias stress. While in the case of off-state stress,  $\beta$  is larger for higher  $V_{\text{DS}}$  (as shown in Fig. 5(b),  $\beta = 5.9$ for  $V_{\text{DS}} = 280$  V and  $\beta = 6.5$  for  $V_{\text{DS}} = 270$  V @ $V_{\text{DG}} = 295$  V). The higher  $V_{\text{DS}}$  will bring more electron from 2DEG channel into the GaN layers, resulting in an increasing defects generation rate and larger  $\beta$  value. Compared to off-state stress,  $\beta$ for negative gate bias stress is definitely smaller which means that the breakdown time is much dispersion. This is in consistence with the first breakdown in dielectric due to the more crowding of electric field around the gate under negative gate bias as reflected in the simulation results below.

# **3.2.** Insight into the breakdown mechanism of the two types of stress conditions

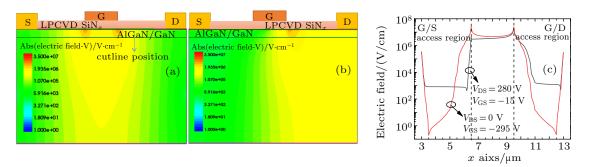

Simulations for rapid breakdown conditions ( $@V_{DG} = 295$  V) verify that negative bias stress will induce significant peak electric field under both edges of gate–drain edge and gate–source, and the peak electric field for gate–source is slightly higher than that of gate–drain even for the device with  $L_{gs} = L_{gd}$  (Figs. 6(a) and 6(c)), which implies that the formation of per-location paths is most likely to occur under the edge of gate–source. While peak electric field for off-state stress is mainly localized at the edge of gate–drain (Figs. 6(b) and 6(c)). In the whole, the peak electric field of both edges of gate–drain edge and gate–source for negative bias stress are higher than that of the edge of gate–drain for off-state stress (Fig. 6(c)).

Fig. 6. Simulation of electric field distribution for rapid breakdown under (a) negative bias stress  $@V_{DG} = 295$  V and (b) off-state stress  $@V_{DG} = 295$  V. (c) Extraction of electric field distribution at the cutline of 10 nm below SiN<sub>x</sub>/AIGaN interface for both of the two stress conditions.

For further underlying the time-dependent breakdown mechanism of negative bias and off-state stress for GaN MIS-HEMT with LPCVD  $SiN_x$  dielectric, a large drain to gate voltage stress (in this paper,  $V_{DG} = 200$  V is adopted) sufficient to generate large numbers of defects but not enough to cause rapid breakdown of device is selected to monitor the long-term evolution of electric parameters.

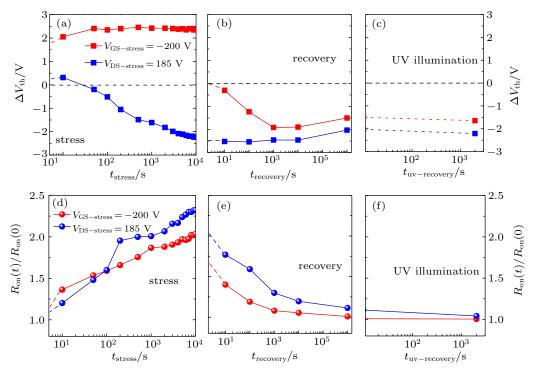

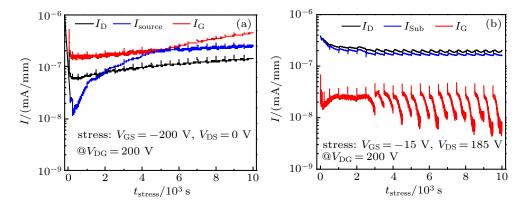

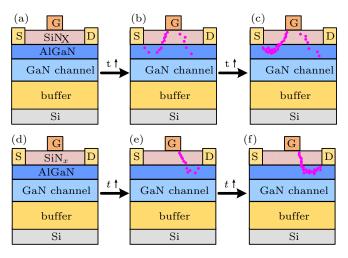

During negative bias stress ( $V_{GS} = -200$  V,  $V_{DS} = 0$  V, @ $V_{DG} = 200$  V as shown in Fig. 7(a)) process, the threshold voltage shift to the positive ( $\Delta V_{\text{Th}} = 2.45$  V after stressed for 10000 s), and on-resistance ( $R_{\text{on}}$ ) continues to increase (Fig. 7(b)) in the whole time stress window. Under negative bias, the injection of electron from gate will be trapped by the pre-existing defects in SiN<sub>x</sub> dielectric, AlGaN barrier and buffer layers.<sup>[14,22]</sup> Those electrons will deplete the 2DEG channel and shift the threshold voltage positively. Moreover, the leakage monitoring (Fig. 8(a)) shows that from 100 s to 10000 s, the leakage of gate ( $I_{\text{GS}}$ ) and drain to gate ( $I_{\text{DG}}$ ) increase about 0.3 and 0.5 order of magnitude gradually. Strikingly, the leakage of source to gate ( $I_{SG}$ ) increases about 1.0 order of magnitude and exceeds  $I_{DG}$  gradually, which further indicates that despite the existence of two peak electric under the gate edges of source and drain for the MIS-HEMT with  $L_{gs} = L_{gd}$ , breakdown for negative bias stress occurs mainly concentrated below the edge of gate–source. After adequate recovery process (after the static storage of 10<sup>6</sup> s and then illuminated under ultraviolet light for 10<sup>4</sup> s), significant negative shift of  $V_{th}$  ( $\Delta V_{Th} = -2.2$  V as shown in Figs. 7(c) and 10(a)) and about 0.5 order of magnitude (Fig. 8(a)) increasing of  $I_{GS}$  underlying that the newly generated defects occurs in the SiN<sub>x</sub> and SiN<sub>x</sub>/AlGaN interfaces. Besides, the negligible degradation of on-resistance ( $R_{on}$ ) after adequate recovery process (Fig. 7(f)) reflects the fact that the newly generation of defects are mainly located at the gate edges of source and drain. Therefore, combined with simulation results as Figs. 6(b) and 6(c), the formation of per-location paths will be first formed in SiN<sub>x</sub> dielectric and then in AlGaN barrier below the edge of gate–source (as shown in Figs. 9(a)–9(c)).

Fig. 7. The evolution of threshold voltage and on resistance during stress and recovery conditions of  $V_{GS} = -200$  V,  $V_{DS} = 0$  V, and  $V_{GS} = -15$  V,  $V_{DS} = 185$  V  $@V_{DG} = 200$  V.

Fig. 8. The evolution of leakage during (a) negative gate bias at  $V_{GS} = -200$  V,  $V_{DS} = 0$  V @ $V_{DG} = 295$  V and (b) off-state stress at  $V_{GS} = -15$  V,  $V_{DS} = 185$  V @ $V_{DG} = 200$  V.

While the negative shift of  $V_{\text{th}}$  ( $\Delta V_{\text{Th}} = -2.35$  V after stressed for 10<sup>4</sup> s as shown in Fig. 7(a)) for off-state stress ( $V_{\text{GS}} = -15$  V,  $V_{\text{DS}} = 185$  V, @ $V_{\text{DG}} = 200$  V) is mainly on account of the gradually generation of new defects of dielectric, more inherent mechanisms are related to gate to source leakage ( $I_{\text{GS}}$ ) as shown in Fig. 8(b), the correlation analysis will be given below. The continued increase of  $R_{\rm on}$  (Fig. 7(b)) during time stress reflects the trapping process in gate to drain access region. Similarly to negative bias stress, after adequate recovery process, the exhibited negative shift of  $V_{\rm th}$ ( $\Delta V_{\rm Th} = -1.85$  V for off-state stress as shown in Figs. 7(f) and 10(b)) and about 0.5 orders of magnitude (Fig. 10(b)) increasing of  $I_{GS}$  underlying that new defects were initially generated in the SiN<sub>x</sub> dielectric. In addition, the negligible change of onresistance ( $R_{on}$ ) after adequate recovery process (Fig. 7(f)) reflects the fact that the newly generations of defects are mainly located under the edge of gate to drain (as shown in Figs. 9(e)– 9(g)).

**Fig. 9.** The schematic mechanism for the negative bias stress (a)–(c) and off-state time-dependent breakdown process (e)–(g).

**Fig. 10.** Transfer characteristics and  $I_{GS}$  before stress and after adequate recovery of (a) negative bias stress at  $V_{GS} = -200$  V,  $V_{DS} = 0$  V @ $V_{DG} = 200$  V and (b) off-state stress at  $V_{GS} = -15$  V,  $V_{DS} = 185$  V @ $V_{DG} = 200$  V.

During off-state stress period of  $10^4$  s (Fig. 8(b)), the drain leakage current is dominated by drain to substrate current ( $I_{Sub}$ ), while the change of  $I_{Sub}$  during the whole stress period is negligible. When the stress time exceeds 2500 seconds,

$I_{\text{DG}}$  gradually decreases during each stress period from beginning to the end, which is attributed to electrons trapped by the localized defects inhibiting the trapping process. Then  $I_{\text{GS}}$  recovers to the initial value at the beginning of next stress period by the reason of electron–electron de-trapping. Moreover,  $I_{\text{GS}}$ is smaller than the previous one after each stress period, which is apparently account of the newly generated defects in SiN<sub>x</sub> dielectric capturing more electrons and further inhibiting the trapping process.

### 4. Conclusion

In conclusion, the evaluations of stress voltage on the time-dependent breakdown characteristics for GaN MIS-HEMT with LPCVD  $SiN_x$  gate dielectric are investigated by combining experiment and simulation.  $SiN_x$  dielectric deliveres excellent long-term negative bias breakdown property. The lifetime extrapolation for 20 years based on 1/E model with failure rate of 63.2% and 0.01% are 209 V and 162 V, respectively. Furthermore, the time-dependent breakdown was investigated under both negative gate bias and off-state stress. For negative bias stress, the breakdown time distribution ( $\beta$ ) decreases with the increase of negative gate voltage, because more electrons will inject into the dielectric and introduce more defects under a higher bias, thus fewer formed defects are needed for the per-location paths for higher negative gate bias stress. While  $\beta$  is larger at higher drain voltage for offstate stress, which means that higher  $V_{DS}$  will bring more electrons from 2DEG channel into the GaN layers, resulting in an increasing defects generation rate and larger  $\beta$  value. Two humps in the time-dependent gate leakage occurred during both breakdown conditions, which can be ascribed to the different newly generated leakage paths at different locations. Combining experiment and simulation results, the catastrophic breakdown of  $SiN_x$  dielectric will be triggered first, and then the GaN layer breakdown will occur subsequently. The peak electric field under the gate edges of source and drain is confirmed as main locations for the breakdown of negative gate voltage stress and off-state stress, respectively.

### References

- Moens P, Liu C, Banerjee A, Vanmeerbeek P, Coppens P and Ziad H 2014 Proc. Int. Symp. Power Semicond. Dev. and ICs. 6 374

- [2] Li L, Zhang J, Liu Y and Ao J 2016 Chin. Phys. B 25 038503

- [3] Hua M, Liu C, Yang S, Liu S, Fu K, Dong Z, Cai Y, Zhang B and Chen K 2015 IEEE Electron Device Lett. 36 448

- [4] Cook T, Fulton C, Mecouch W, Davis R, Namanich R 2003 Appl. Phys. 94 3949

- [5] Zhang Z, Qin S, Fu K, Yu G, Li W, Zhang X, Sun S, Song L, Li S, Hao R, Fan Y, Sun Q, Pan G, Cai Y and Zhang B 2016 *Appl. Phys. Express* 9 084102

- [6] Hua M, Qian Q, Wei J, Zhang Z, Tang G and Chen K 2018 Physica Status Solidi (a) 215 1700641

- [7] Hua M, Liu M, Yang S, Liu S, Fu K and Dong Z 2015 Trans. Electron Dev. 62 3215

- [8] del Alamo J, Guo A and Warnock S 2017 Journal of Materials Research 32 3458

- [9] Meneghini M, Rossetto I, Bisi D, Ruzzarin M, Hove M, Stoffels S, Wu T, Marcon D, Decoutere S and Meneghesso G 2016 *IEEE Electron Dev. Lett.* 37 474

- [10] Marcon D, Meneghesso G, Wu T, Stoffels S, Meneghini M, Zanoni E and Decoutere S 2013 IEEE Trans. Electron Dev. 60 3132

- [11] Wamock S and del Alamo J 2017 IEEE IRPS 4 B-3-1

- [12] Yang W, Yuan J, Krishnan B and Shea P 2019 IEEE 7th WiPDA 277

- [13] Hua M, Wei J, Bao Q, Zhang Z, Zheng Z and Chen K 2015 IEEE Electron Dev. Lett. 39 413

- [14] Guo A and del Alamo J 2016 IEEE IRPS 4 A-1-1

- [15] Que T, Zhao Y, Li L, He L, Qiu Q, Liu Z, Zhang J, Chen J, Wu Z and Liu Y 2020 *Chin. Phys. B* 29 037201

- [16] Song L, Fu K, Zhao J, Yu G, Hao R, Fan Y, Cai Y and Zhang B 2018 J. Vac. Sci. & Technol. B 36 042201

- [17] Qi Y, Zhu Y, Zhang J, Lin X, Cheng K, Jiang L and Yu H 2018 IEEE Trans. Electron Dev. 65 1759

- [18] Jauss S, Hallaceli K, Mansfeld S, Schwaiger S, Daves W and Ambacher O 2017 IEEE Trans. Electron Dev. 64 2298

- [19] Warnock S and del Alamo J 2016 IEEE IRPS 4 A-6-1

- [20] Warnock S and del Alamo J 2017 IEEE IRPS 4 B-3.1

- [21] Degraeve R, Kaczer B and Groeseneken G 1999 Microelectronics Reliability 39 1445

- [22] Jin D, Joh J, Krishnan S, Tipirneni N, Pendharkar S and del Alamo J 2013 IEEE IEDM 6 2.1